웨이퍼 백그라인딩(Wafer Backgrinding) - 반도체 후공정

웨이퍼 백그라인딩(Wafer Backgrinding)은 웨이퍼의 뒷면을 갈아(grinding) 얇게 만드는 공정으로 반도체 후공정의 시작이라 할 수 있다. 웨이퍼 백그라인딩 공정은 웨이퍼 두께를 줄이고, Frontend와 Backend 공정을 연결하여 두 공정 간의 문제를 해결할 수 있다. 반도체 칩이 얇을수록 더 많은 칩을 쌓을 수 있고 집적도도 높아지나, 집적도가 높아지면 제품 성능이 저하될 수 있기 때문에 웨이퍼 두께를 결정하는 그라인딩 방식은 반도체 칩 원가 절감과 제품 품질을 결정하는 핵심 요소 중 하나라고 할 수 있다. 웨이퍼 백그라인딩은 "backlap", "backfinish", "back side grinding", "wafer thinning" 등으로 불리기도 한다.

백그라인딩 공정을 통해 전공정에서 화학적으로 오염된 부분을 제거하고 칩 두께를 줄일 수 있어, IC 카드나 모바일 장치에 탑재되는 얇은 칩을 만드는 데 매우 적합하게 가공한다. 또한 백그라인딩 공정은 저항 감소, 전력소모 감소, 열전도도를 높여 웨이퍼 후면으로 열을 빠르게 발산시키는 장점도 가지고 있다. 이와 같은 백그라인딩 공정은 전자제품이 소형화됨에 따라 지속적으로 중요해지고 있다. 그러나 동시에 웨이퍼의 두께가 얇아지기 때문에 외력에 의해 깨지거나 휘어지기 쉬워 공정 단계가 더 어려워지는 문제점도 존재한다.

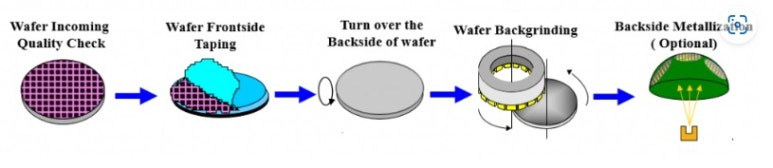

그림. 웨이퍼 라미네이션, 백그라인딩 공정 (출처 : https://mauricegroklein.blogspot.com/)

상세 공정

백 그라인딩은 웨이퍼에 보호 테이프를 적용하는 단계(Tape Lamination)와 웨이퍼 뒷면을 연마하는 단계로 나뉘어지며, 백그라인딩 종료 후 웨이퍼에서 칩을 분리하기 전에 보호 테이프로 웨이퍼 마운팅에 웨이퍼를 올려놓게 된다.

Tape Lamination은 웨이퍼 전면에 테이프를 붙이는 코팅 공정이다. 백 그라인딩을 할 때 실리콘 화합물이 주변으로 확산되고 이 과정에서 외력으로 인해 웨이퍼가 크랙되거나 뒤틀릴 수도 있으며, 웨이퍼 면적이 클수록 이 현상에 더 취약해지기 때문에, 연마공정 전에 웨이퍼를 보호하기 위해 얇은 UV 청색 필름을 도포하는 공정을 말하는 것이다.

라미네이션시 필름을 적용할 때 웨이퍼와 테이프 사이의 틈이나 기포를 방지하기 위해 접착력을 향상시킬 필요가 있으나, 연삭이 완료된 후에는 웨이퍼의 테이프를 자외선에 노출시켜 접착력을 줄여서 쉽게 탈 리가 가능하게 해야 한다. 또한, 박리 후 테이프 잔여물이 웨이퍼 표면에 남아 있지 않도록 해야 한다.

Back Grinding 후 Wafer의 두께는 일반적으로 800-700 ㎛에서 80-70 ㎛로 감소하여, 4~6층으로 적층할 수 있게 된다. 최근에는 2회 연마하는 공정을 통해 웨이퍼를 50㎛ 이하로 줄여 16~32단으로 쌓을 수 있게 하기도 한다. 또한 이와 같은 백 그라인딩은 2~3 정도의 단계를 걸치기도 하며, 이 때 슬러리와 탈이온수 등을 추가하여 연마하기도 한다.

또한, 1차 그라인딩 전에 웨이퍼를 반으로 자르는 DBG(Dicing Before Grinding) 방식을 사용하는 경우가 있는 등 공정은 경우 따라 다양하게 변경된다.