PoP(Package on a Package) & SiP(System in a Package) 반도체(Semiconductor)

PoP(Package on a Package)

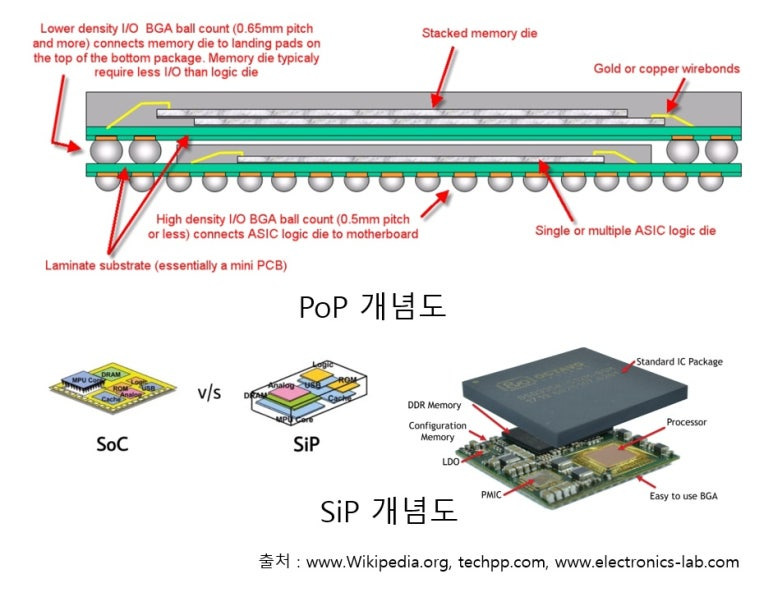

PoP(Package on a Package)는 개별 로직과 BGA(Memory Ball Grid Array - Ball의 형태로 집적회로를 연결하는 기법) 2개의 집적회로 패키지들을 수직으로 결합(적층)하는 패키징 방법이다. 이들 간에 신호를 라우팅하기 위한 표준 인터페이스가 있으며, 이를 통해 휴대폰, PDA(Personal Digital Assistant) 및 디지털 카메라와 같은 장치에서 약간 두께에 대한 요구 사항을 희생하는 대신 더 높은 구성 요소 밀도를 얻을 수 있다. 그러나, 2개 이상의 패키지가 있는 스택은 방열 등의 고려 사항 때문에 일반적이지 않다. PCB 조립 중에 PoP 스택의 하단 패키지는 PCB에 직접 배치되고 스택의 다른 패키지는 상단에 적층되는 형태로 구성되는 경우가 많다.

PoP에 대해 널리 사용되는 두 가지 구성이 있다.

가. 순수 메모리 스태킹: 두 개 이상의 메모리 전용 패키지를 적층하는 것이다.

나. 혼합 로직-메모리 스태킹: 하단에는 로직(CPU) 패키지, 상단에는 메모리 패키지를 적층하는 것인대, 예를 들어 아래쪽은 휴대폰용 SoC(시스템 온 칩) 등을 연결하는 것을 들 수 있다. 일반적으로 로직 패키지(메모리 패키지와 반대)는 마더보드에 더 많은 BGA 연결이 필요하기 때문에 맨 아래에 위치시킨다.

장점과 단점

PoP 기술은 기존 Packaging 기술의 장점과 다이 스태킹 기술의 이점을 결합하려고 시도하면서 단점을 피하려고 한다. 기존 패키징은 각 패키지를 PCB에 직접 나란히 배치하는 일반 PCB 조립 기술을 위해 설계된 패키지인 자체 패키지에 각 다이를 배치한다. 3D 다이 스태킹 시스템 인 패키지(SiP) 기술은 단일 패키지에 여러 다이를 적층하며, 이는 기존 PCB 어셈블리에 비해 몇 가지 장점과 몇 가지 단점이 있다.

PoP의 가장 분명한 이점은 마더보드 공간 절약이다. 즉 전기적으로 PoP는 컨트롤러 및 메모리와 같은 서로 다른 상호 운용 부품 사이의 트랙 길이를 최소화할 수 있다. 이는 회로 간 상호 연결의 라우팅이 짧을수록 신호 전파가 빨라지고 잡음 및 누화가 줄어들기 때문에 장치의 전기적 성능이 향상되는 것을 의미한다.

또한 PoP에서 Memory 칩과 Logic 칩이 분리된다는 것도 장점의 하나이다. 즉, PoP 조립시 메모리 패키지는 logic 패키지와 별도로 테스트할 수 있으며, 메모리가 불량인 경우 메모리만 폐기될 수 있으며, 심지어 서로 다른 공급업체의 메모리를 사용할 수도 있다. 또한 PoP 조립시 이론적으로는 기계적으로 결합 가능한 모든 메모리 구성을 사용할 수도 있다. 이것은 최종 제품의 조립자가 재고 관리 등을 단순하게 할 수 있다.

임베디드PoP 기술 : 칩은 패키지 하단의 기판에 내장되어 있어서, 더 짧은 전기 연결로 더 작은 패키지를 가능하게 한다. ASE(Advanced Semiconductor Engineering)와 같은 회사의 지원을 받아 개발되었다.

표준화 : JEDEC(국제 반도체 표준화 기관) JC-11 위원회(Committee)는 하단 PoP 패키지와 관련된 패키지 개요 도면 표준을 다루며, JEDEC JC-63 위원회는 상단(메모리) PoP 패키지 핀아웃 표준화를 다룬다.

SiP(System in a Package)

SiP(System in a Package) 또는 System-in-Package는 하나의 칩 캐리어 패키지에 전체 시스템의 기능을 수행할 수 있는 다수의 IC 패키지 기판이나 부품을 포함하는 여러 IC(집적 회로)이다. IC는 패키지에 패키지를 사용하여 적층하거나, 나란히 배치하거나, 기판에 내장할 수 있다. SiP는 전자 시스템의 모든 또는 대부분의 기능을 수행하며, 일반적으로 휴대폰, 디지털 음악 플레이어 등의 구성 요소를 설계할 때 사용된다. 집적 회로를 포함하는 다이는 패키지 기판에 수직으로 적층될 수 있으며, 패키지 기판에 접착 된 미세한 와이어로 내부적으로 연결되거나, 플립 칩 기술을 사용하면 솔더 범프를 사용하여 적층 칩을 패키지 기판에 결합할 수 있다. 혹은, 두 기술을 모두 단일 패키지에 사용할 수 있다. 물론, SiP는 SoC(Systems on a Chip)와 비슷하지만 덜 긴밀하게 통합되어 있으며 단일 반도체가 아니라는 것에 차이가 있다.

SIP을 이용하여, 시스템 크기를 줄이거나, 성능을 개선하거나, 비용을 절감할 수 있다. SiP는 MCM(Multi Chip Module) 기술에서 발전했으며, SiP도 여러 칩을 쌓거나 다이를 서로 위에 쌓는 다이 스태킹을 사용할 수 있다.SiP 솔루션에는 플립 칩, 와이어 본딩, 웨이퍼 레벨 패키징, TSV(Through-silicon via), 칩렛 등과 같은 여러 패키징 기술이 사용될 수 있다.

SiP 다이는 칩렛 또는 퀼트 포장과 같은 기술을 사용하여 수직으로 쌓거나 수평으로 타일링할 수 있다. SiP는 실리콘 관통 비아를 사용하여 다이를 통과하는 도체와 적층된 실리콘 다이를 연결하는 약간 더 조밀한 3차원 집적 회로와 달리 표준 오프칩 와이어 본드 또는 솔더 범프로 다이를 연결한다. 상당히 표준적인 칩 다이를 조밀한 영역에 적층하기 위해 다양한 3D 패키징 기술이 개발되었다. SiP는 특수 프로세서, DRAM, 플래시 메모리와 같은 여러 종류의 칩 또는 다이를 포함할 수 있으며, 모두 동일한 기판에 장착된 수동 부품(저항기 및 커패시터)과 결합될 수 있다. 즉, 완전한 기능 단위를 단일 패키지로 구축할 수 있으므로 작동하기 위해 추가할 외부 구성 요소가 거의 없게 설계할 수 있다. 이는 MP3 플레이어 및 휴대폰과 같은 공간 제약이 있는 환경에서 인쇄 회로 기판 및 전체 설계의 복잡성을 줄이기 때문에 특히 유용할 수 있다. 이러한 이점에도 불구하고 SiP는 패키지 내의 다른 모든 모듈이 작동하더라도 패키지의 결함 있는 칩으로 인해 전체가 작동하지 않을 수 있기 때문에 제조 수율이 감소할 수 있다.

SiP와 SoC의 차이점

SiP는 기능을 기반으로 구성 요소를 단일 회로 다이(혹은 칩)에 통합하는 일반적인 SoC(System on a Chip) 집적 회로 와 구분된다. SoC는 일반적으로 CPU, 그래픽 및 메모리 인터페이스, 하드 디스크 및 USB 연결, 랜덤 액세스 및 읽기 전용 메모리, 보조 스토리지 및/또는 컨트롤러를 단일 다이에 통합한다. 이에 비해 SiP는 이러한 모듈을 하나 이상의 칩 패키지 또는 다이에서 개별 구성 요소로 연결한다. SiP는 기능에 따라 구성 요소를 분리하고 중앙 인터페이스 회로 기판을 통해 연결한다는 점에서 일반적인 기존 마더보드 기반 PC 아키텍처와 유사하다고 할 수 있으며, 따라서 SiP는 SoC에 비해 통합 등급이 낮다고 볼 수 있다.